Journal of Chemical and Pharmaceutical Sciences

# VLSI Configuration of Yielding Resolution Low Concentration Equality Ensure Cipher for Squat Control

V. Srinivasan\*, M. Sundararajan Department of ECE, Bharath University, Chennai

\*Corresponding author: E-Mail: Chennai.srinivasan.etc@bharathuniv.ac.in

## ABSTRACT

In this paper depicts a successful methodology for LDPC (Low Concentration Equality ensure cipher) decoder structural engineering for low power applications. In the LDPC decoder is a direct blunder revising code, a technique for transmitting a message over a boisterous transmission channel. The delicate choice strategy was utilized for proficient mistake amendment and location. A Posteriori Probability (APP) memory was utilized to store the information. However APP memory is more number of tiles utilized as a part of LDPC decoder. So the force utilization was expanded. The critical components of this work, for example, the quantity of tiles was decreased into single tiles utilizing location seeking strategy. Because of the diminishment of the tiles Compared to the current LDPC decoder the force utilization will be diminished additionally throughput is diminished. The proposed decoder which uses the base information generator unit with arbitrary entomb leaver, can be identify and right the multi bit blunder additionally low power utilization and high throughput.

KEY WORDS: Low Density Parity Checker, Address searching method, A Posteriori Probability memory.

## **1. INTRODUCTION**

The most alluring element of low-thickness equality check (LDPC) codes is their capacity to accomplish a noteworthy division of the channel limit utilizing iterative interpreting at generally low usage multifaceted nature. Limited geometry LDPC codes can be developed and abbreviated in different approaches to get other great LDPC codes. Since quite a while ago broadened limited geometry LDPC codes have been developed and they accomplish an execution just a couple of tenths of a decibel far from the Shannon hypothetical point of confinement with iterative unraveling.

Cell-to-cell impedance has been all around perceived as a noteworthy clamor source in charge of crude memory-stockpiling unwavering quality debasement. As the unwavering quality is a basic issue for new era multi-level cell (MLC) streak recollections, there is developing call for quick and conservative blunder redress code (ECC) circuit with least effect on memory access time and chip territory. It delivers high-throughput and low-power ECC plan for MLC NAND glimmer memories.

Evaluated factual data is exceptionally valuable when choosing the exactness of memory get to and deciding the detecting reference voltages for both hard and delicate choice blunder remedy in NAND blaze memory. A piece joining plan that boosts rationale usage and expansions the decoder throughput contrasted and ordinary plans. This system requires no adjustment in the structure of the code or the interpreting calculation.

Limited geometry LDPC codes can be decoded in different routes, extending from low to high translating many-sided quality and from sensibly great execution. They perform extremely well with iterative interpreting. Moreover, they can be placed in either cyclic or semi cyclic structure. Consequently, their encoding can be accomplished in straight time and actualized with basic criticism shift registers.

Limited geometry LDPC codes can be broadened and abbreviated in different approaches to get other great LDPC codes. One may contend that the disservice of serial timetables is that they don't consider a parallelized decoder equipment execution because of their serial nature, while the flooding calendar can be completely parallelized. On the other hand, the serial timetable can be in part parallelized. Messages from sets of hubs can be overhauled at the same time.

The paper is composed as takes after. In Section 2, the proposed LDPC decoder outline is clarified. In Section 3, the location looking strategy is displayed; the force utilization and throughput is assessed. In Section 4, recreation results are talked about. In Section 5, finishes up the paper.

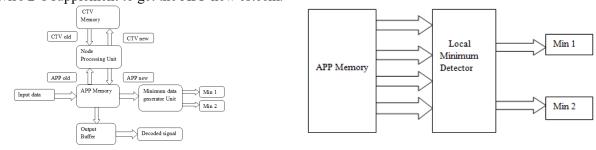

**Proposed LDPC Decoder Design**: LDPC decoder construction modeling is least information generator unit plan is proposed. Location looking technique utilized as a part of the configuration. The proposed LDPC decoder lessens the force utilization and high throughput. LDPC decoder building design appeared in Fig.1. Modules in LDPC decoder:

- Minimum information generator unit.

- Node Processing Unit.

- APP Memory.

- Output Buffer.

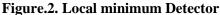

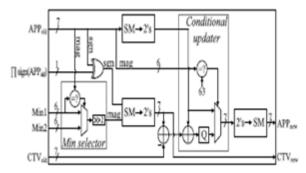

**Nearby Minimum Detector:** Application Memory has been more tiles utilized and nearby least identifier to be two littlest quality. Appeared in Fig.2.It has utilizing 4:2 converter to locate the littlest worth for most extreme quality

July - September 2016

#### ISSN: 0974-2115

#### www.jchps.com

## Journal of Chemical and Pharmaceutical Sciences

does not fulfill the mistake amendment. So will be take two littlest quality for Min1 and Min2. Min1 and Min2 worth to send the NPU (Node Processing Unit) and afterward sign additionally size quality for NPU, sign quality has beginning take for 1bit.remaining 6bits for extent appeared in Fig.3.To take 2"s supplement change over whole number worth to double esteem. At last APP Memory gets the 7bits new esteem. The size quality is equivalent to one estimation of min selector obstruct in that esteem is min10therwise is equivalent to min2 and contingent updater piece likewise 2"s supplement to get the APP new esteem.

Figure.1. LDPC decoder architecture

## Figure.3. Converter structure

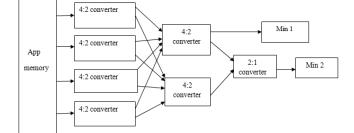

Least information generator unit: It is the crude bury leaver produced through haphazardly selecting the locations over a scope of square size. They don't bear any structure and the principle drawback is that once created through some arbitrary capacity, they can't be repeated Hence the best way to utilize them in genuine equipment is to remember the arrangement and use it as a LUT (lookup table). Minimum information generator unit with irregular bury leaver to gives littlest worth in the hub preparing unit. To decrease the burst mistake rate and low power utilization A quality "qc" is created at each clock cycle and encouraged to the base information generator unit (MDGU). Then, "qc" is contrasted with the upgraded first and second least (min1 and min2), that are introduced as the most extreme permitted worth toward the start of every check hub stage appeared in fig.4. The least of both correlations (min1\_new and min2\_new) is gone on and inspected on the rising edge of the clock signal, together with the past first least and a banner flagging. In the event that min1 $\neq$ min1\_new.If min1\_update=0, then min2\_new is substituted with past estimation of min1. At long last, min1 and min2 are redesigned on the falling edge of the clock, prepared and stable for the following "qc".

Figure.4. Minimum data generator unit

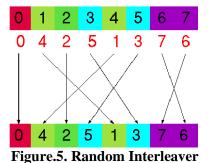

Random Interleaver: Input sequence

July - September 2016

www.jchps.com

#### Interleaved sequence

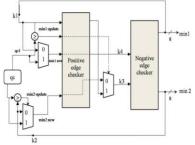

The CTV memory between min1, min2 and greatness esteem thought about is equivalent right moved by 2bits.the sign size quality takes 2's supplement, to get the CTV new esteem.

### Figure.6. Structure of Node Processing Unit

**CTV memory and output buffer:** CTV (Check to variable) Memory is stored the value and the read 0, write 1 is output buffer send the 7bits decoded signal. Node Processing Unit provide the old value and CTV is stored the value also new value the needs of NPU to provide new value. The output buffer is read one and write zero the result is decoded signal otherwise the value is stored in App memory.

**Low Power APP memory**: Low Power APP Memory with validation memory to reduce the power consumption. Input data to send 7bits for Low power APP memory and throughput is decreased for conventional method. It Consists of two memories:

- VM (Validation Memories).

- Validation memory means that memory in working period.

- OATAM (Original Address Table address Memories).

Validation memory above diagram the searching address VM21 is 01 the output is 1 and VM22 is 10 also 1. Table 1 VM21 and VM22 is the searching address 00, 11. The output of AND gives respectively 0,1 shown in Fig. 6. Address searching method: App memory is number of tiles reduced into single tiles

Using address searching method.

| Table.1. Layer searching table |                   |      |      |               |

|--------------------------------|-------------------|------|------|---------------|

| Address Index                  | Searching Address | VM21 | VM22 | Output of AND |

| 0                              | 00                | 1    | 0    | 0             |

| 1                              | 01                | 1    | 0    | 0             |

| 2                              | 10                | 0    | 1    | 0             |

| 3                              | 11                | 1    | 1    | 1             |

## Table.1. Layer searching table

Figure.6. Address Searching using Layer1 Architecture Table.. OATAM21 Address Generation Table

| Output of AND | OATAM21 | <b>Original address</b> |

|---------------|---------|-------------------------|

| 1             | 00      | 10                      |

| 1             | 01      | 11                      |

| 1             | 10      | 01                      |

| 1             | 11      | 00                      |

Table 2.The output of AND is 1.the OATAM 21 address gives 00 ,11 respectively the Original address is 10, 00.

#### ISSN: 0974-2115

Journal of Chemical and Pharmaceutical Sciences

| Table.5. OATAWI22 Address Generation Table |         |                  |  |  |

|--------------------------------------------|---------|------------------|--|--|

| <b>Output of AND</b>                       | OATAM22 | Original address |  |  |

| 1                                          | 00      | 01               |  |  |

| 1                                          | 01      | 11               |  |  |

| 1                                          | 10      | 00               |  |  |

| 1                                          | 11      | 10               |  |  |

Table.3. OATAM22 Address Generation Table

Table.3 Similarly OATAM22 address gives 01, 10.the original address is 11, 00.

# 2. RESULTS AND DISCUSSION

The proposed LDPC decoder technique contrasted and the current outline. The force utilization and throughput of proposed configuration gives preferable result over existing LDPC decoder outline. The created code is integrated in Xilinx Pack 9.1 for Virtex 4 gadget. The equipment synopsis is gotten for every strategy execution log record of Xilinx 9.1 venture guide appeared in Fig.7.

| Xilina XPeener - [LSPC.port]                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                      |                                                   |            |           |                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The ER New York Window 1980                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                      |                                                   |            |           |                                                                                                                                                                                                                |

| 944 DS A                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                      |                                                   |            |           |                                                                                                                                                                                                                |

| Watege M Carnet (a)         Press (a)         P           Yout         1.2         0.0         0.0           Down         0.0         0.00         0.0           Second         0.5         0.0         0.0           Symm         0.0         0.00         0.00           Symm         0.0         1.00         0.00           Second         7.25         10.01         0.00           VersB         2.5         5         5         5 | Palanze 9.21 - IBower<br>Cupyings 00 1885-00<br>Design: Crizilio<br>Preferences: LBC.pts<br>Part: Writing<br>Data variation abunch<br>Prover namery: | 17 Biling, Inc<br>selectionCollin<br>1<br>1943-52 | All rig    |           | ал.                                                                                                                                                                                                            |

| Evenie 640 630<br>Comment 640 630                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                      |                                                   |            | 2.53      |                                                                                                                                                                                                                |

| ddPoe 2234 w                                                                                                                                                                                                                                                                                                                                                                                                                             | Total estimated power                                                                                                                                | 000200011000                                      |            | 1.53      |                                                                                                                                                                                                                |

| annay Poet. Orett. Terral                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                      | Vector 1.209:                                     | 50         | 60        |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      | Youwar 2.500:                                     |            | 190       |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      | Tees25 1.50%                                      |            |           |                                                                                                                                                                                                                |

| Data Views                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                      | lupite:                                           | 0          | 0         |                                                                                                                                                                                                                |

| 🖼 Report Views                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                      | Logics                                            |            |           |                                                                                                                                                                                                                |

| <ul> <li>Powr Tepst (1714.)</li> <li>Powr Tepst</li> </ul>                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                      | (htps://                                          |            |           |                                                                                                                                                                                                                |

| <ul> <li>Power Report</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                      | Veral 8                                           | 0          | 0         |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      | Signals:                                          | ō          | õ         |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      |                                                   |            |           |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      | Perist 1.200v                                     | 50         | 60        |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | Quinescent 1                                                                                                                                         | Promas 1.5071                                     | 77         | 199       |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | Thermal summery:                                                                                                                                     |                                                   |            |           |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          | Estimated Suprisia                                                                                                                                   | Lengeralure:                                      |            | 100       |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      | conjection et al                                  | _          | 144       |                                                                                                                                                                                                                |

| recommendations you explicitly spe-                                                                                                                                                                                                                                                                                                                                                                                                      | apping level (major sil-                                                                                                                             | icon revision)                                    | for this - | using, Th | . Tolers your design in targeted at devices of this stepping level, it<br>is will allow the tools to take advantage of any meniadole performance<br>idditional information on "stepping level" is evaluable at |

| DFD:                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                      |                                                   |            |           |                                                                                                                                                                                                                |

| The power estimate will be calculated                                                                                                                                                                                                                                                                                                                                                                                                    | ad online MildBORD data                                                                                                                              |                                                   |            |           |                                                                                                                                                                                                                |

| The power eminents will be contrain                                                                                                                                                                                                                                                                                                                                                                                                      | es using ADVANCES cola.                                                                                                                              |                                                   |            |           |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      |                                                   |            |           |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      |                                                   |            |           |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                      |                                                   |            |           |                                                                                                                                                                                                                |

# Figure.7. Simulation result for minimum data generator unit

**Figure.8. Force Report**

**Force Report**: This is the force utilization report appeared in Fig.8.The aggregate Power utilization of the LDPC decoder is 253mw.

# Throughput Report: Throughput Report

This is the throughput Report appeared in Fig.9.

- Throughput: The rate at which the information can be exchanged or got through a port for every second.

- Unit: Mb/sec

- Throughput=(Number of Slice Required+ Number of LUT required)/Number of slice\*100 %=(25+45)/25 Mb/sec

- Throughput=2.8Mb/Sec

Figure.9. Throughput Report Table.4. Performance analysis

| <b>Performance parameters</b> | Proposed method | Existing method |

|-------------------------------|-----------------|-----------------|

| Power consumption             | 253mW           | 267mW           |

| Throughput                    | 2.8Mb/sec       | 1.9Mb/sec       |

Table 4.The performance of proposed LDPC decoder architecture is analyzed based on above results.

# 3. CONCLUSION

VLSI configuration of LDPC decoder utilizing least information generator unit with arbitrary entomb leaver. It can be identify and right the multi bit blunders in LDPC decoder. The force utilization and throughput of proposed LDPC decoder configuration gives preferred result over existing outline. So the Power Consumption and throughput of the proposed configuration was measured to be 253mW and 2.8Mb/sec separately. This procedure discovered applications in different fields like Satellite Communication, Digital TV and Under water

#### www.jchps.com REFERENCES

Dong G, Li S and Zhang T, Using data post compensation and pre distortion to tolerate cell-to-cell interference in MLC NAND flash memory, IEEE Trans Circuits Syst I, Reg, 57(10), 2010, 2718–2728.

Gallager R.G, Low-density parity-check codes, IRE Trans Inf Theory, 8(1), 1962, 21–28.

Gallager R.G, Low-Density Parity-Check Codes. Cambridge, MA, USA, MIT Press, 1963.

Gopalakrishnan K, Sundar Raj M, Saravanan T, Multilevel inverter topologies for high-power applications, Middle - East Journal of Scientific Research, 20(12) 2014, 1950-1956.

Gregori S, Cabrini A, Khouri O, and Torelli, On-chip error correcting techniques for new-generation flash memories, Proc. IEEE, 91(4), 2003, 602–616.

Jasmin M, Vigneshwaran T, Beulah Hemalatha S, Design of power aware on chip embedded memory based FSM encoding in FPGA, International Journal of Applied Engineering Research, 10(2), 2015, 4487-4496.

Jonghong Kim and Wonyong Sung, Rate-0.96 LDPC Decoding VLSI for Soft-Decision Error Correction of NAND Flash Memory, IEEE Trans. VLSI Systems, vol. 22(5), 2014.

Kanniga E, Selvaramarathnam K, Sundararajan M, Kandigital bike operating system, Middle - East Journal of Scientific Research, 20(6) 2014, 685-688.

Kanniga E, Sundararajan M, Modelling and characterization of DCO using pass transistors, Lecture Notes in Electrical Engineering, 86(1), 2011, 451-457.

Karthik B, Arulselvi, Noise removal using mixtures of projected gaussian scale mixtures, Middle - East Journal of Scientific Research, 20(12) 2014, 2335-2340.

Karthik B, Arulselvi, Selvaraj A, Test data compression architecture for lowpower vlsi testing, Middle - East Journal of Scientific Research, 20(12) 2014, 2331-2334.

Karthik B, Kiran Kumar T.V.U, Authentication verification and remote digital signing based on embedded arm (LPC2378) platform, Middle - East Journal of Scientific Research, 20(12) 2014, 2341-2345, 2014.

Karthik B, Kiran Kumar T.V.U, EMI developed test methodologies for short duration noises, Indian Journal of Science and Technology, 6(5), 2013, 4615-4619.

Karthik B, Kiran Kumar T.V.U, Vijayaragavan P, Bharath Kumaran E, Design of a digital PLL using 0.35μm CMOS technology, Middle - East Journal of Scientific Research, 18(12) 2013, 1803-1806.

Philomina S, Karthik B, Wi-Fi energy meter implementation using embedded linux in ARM 9, Middle - East Journal of Scientific Research, 20(12), 2014, 2434-2438.

Saravanan T, Sundar Raj M, Gopalakrishnan K, Comparative performance evaluation of some fuzzy and classical edge operators, Middle - East Journal of Scientific Research, 20(12) 2014, 2633-2633.

Saravanan T, Sundar Raj M, Gopalakrishnan K, SMES technology, SMES and facts system, applications, advantages and technical limitations, Middle - East Journal of Scientific Research, 20(12) 2014, 1353-1358.

Sun F, Devarajan S, Rose K, and Zhang T, Design of on-chip error correction systems for multilevel NOR and NAND flash memories, IET Circuits, Devices Syst, 1(3), 2007, 241–249.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, A DFIG based wind generation system with unbalanced stator and grid condition, Middle - East Journal of Scientific Research, 20(8) 2014, 913-917.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, Effective routing technique based on decision logic for open faults in fpgas interconnects, Middle - East Journal of Scientific Research, 20(7) 2014, 808-811.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, Privacy conscious screening framework for frequently moving objects, Middle - East Journal of Scientific Research, 20(8) 2014, 1000-1005.